컴퓨터구조

4. The Processor > 4-6. Exceptions

Exceptions

Updated at 2022.11.03

Code scheduling

There are three types of critical dependencies

- Read after write

- Write after read

- Write after write

If two instructions have one of the above dependencies,

the execution order these two instructions must be maintained

Exceptions

Exceptions VS Interrupts in MIPS

- Exception: arises within the CPU (internally)

- Interrupt: from an external I/O controller (externally)

| Type of event | From where | MIPS terminology |

|---|---|---|

| I/O device request | External | Interrupt |

| Invoke OS from a user program | Internal | Exception |

| Arithmetic overflow | Internal | Exception |

| Using an undefined instruction | Internal | Exception |

| HW malfunctions | Either | Exception or interrupt |

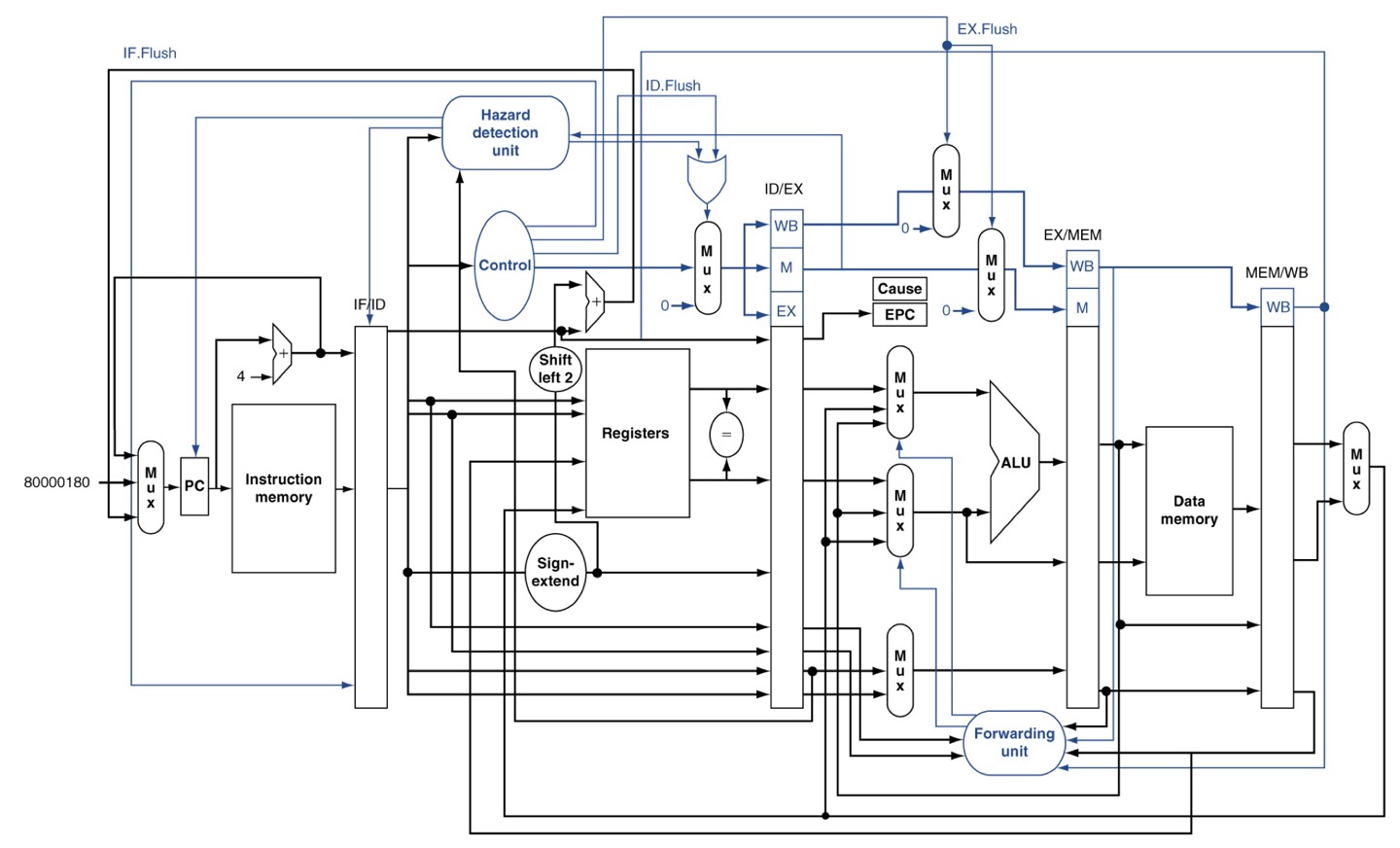

How to handle

- Step 1: Save the address of the offending instruction in the EPC (Exception Program Counter)

- EPC is a 32-bit register

- Step 2: Save the reason for the exception in the Cause register

- Cause is a 32-bit register (some bits are unused)

- Step 3: Jump to the exception handler corresponds to the cause

- The handler address for undefined opcode:

- Overflow:

- But sometimes without saving the reason for the exception, it jumps to the exception handler

- Step 4: Do actions

- Read the cause and determine the action required

- If recoverable, take a corrective action and use EPC to return to a program

- Otherwise, terminate the program and report error using EPC, cause, ...

Exceptions according to the stage

Exceptions can occur in any stage (except WB)

- IF: Invalid memory access (memory fault)

- e.g., when PC holds an invalid memory address value

- ID: Undefined instruction

- e.g.,

abc $t0, $t1, $t2

- e.g.,

- EX: Overflow

- e.g., when we use add, addi, and sub instructions

- MEM: Invalid memory access (memory fault)

- e.g., when a computed target memory address is abnormal

Regardless of the stage, the cause of exceptions is stored in the Cause register

Then, guess which instruction caused the exception based on the cause

Multiple exceptions

Multiple instructions are executed in different stages at the same time, which means multiple exceptions can occur in the same clock cycle.

How to prioritize multiple exceptions?

- In MIPS, earliest instruction first

- Flush subsequent instructions