컴퓨터구조

5. Memory Hierarchy > 5-4. Virtual memory Part 2

Virtual memory Part 2

Updated at 2022.11.24

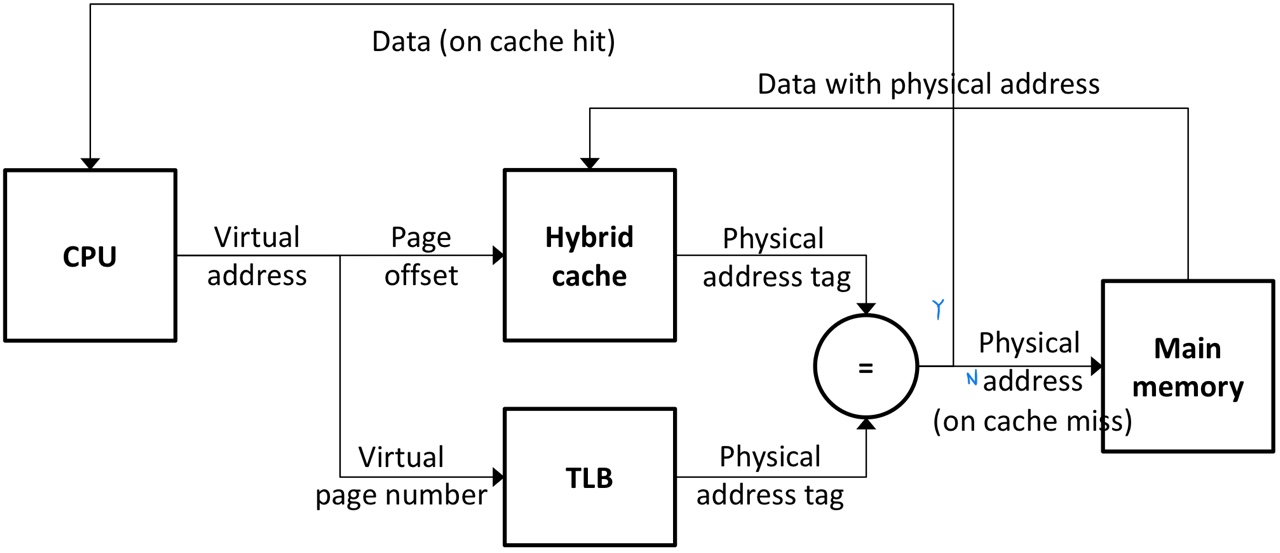

Integrating TLB, Cache, Memory

Aliasing in virtually addressed cache

- The same virtual address of different processes can be mapped to different physical address

- Wrong cache hit can occur

- Different virtual addresses of different process can be mapped to the same physical address

(when some memory space is shared by multiple processes)- The physical memory can be cached in two different locations

- Coherency problem can happen

One program writes the data without the other program being aware that the data had changed

Simple solution

- Flush cache at context switching -> too high miss rate

- Context switch: In multi-process environments, multiple processes share a single CPU

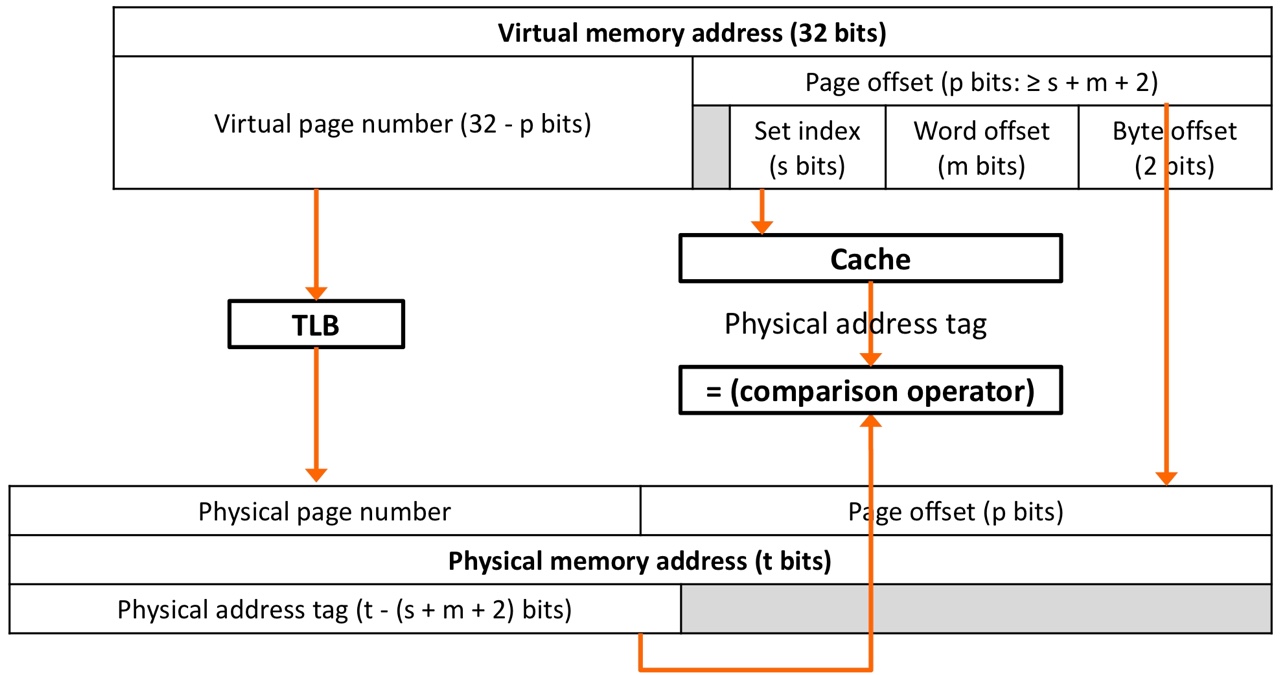

Hybrid cache: virtually-indexed & physically-tagged cache

- No aliasing problem

- TLB & cache are accessed in a parallel manner (fast)

- 32-bit virtual address

- Page size = Bytes

- Physical memory size = Bytes (t-bit physical address)

- Block size = words

- Num of sets in a cache = sets

Typical multi-level cache setup with TLB

- Typical L-1: hybrid cache (virtually-addressed, physically tagged)

- To reduce hit time and miss rate

- Typical L-2: physically-addressed cache

- For simple implementation

- In addition, usually L-2 si large

So, because p < s + m + 2, we cannot use hybrid cache